Lamanya sebuah periode atau garis atau nyala atau mati yang digambarkan dalam skema diatas adalah tergantung, artinya semakin panjang garisnya maka semakin lama pula rentang waktunya.

Jika pada gambar disamping menunjukan bahwa dari kedudukan OFF ke ON atau sebaliknya, ini membutuhkan waktu.

PENCACAH DENGAN MODUL

TABEL OUTPUT

TONE DECODER

SET RESET (RS) FLIP-FLOP

Tabel Kebenaran

Keterangan :

x = tidak diperkenankan

# = sama dengan keadaaan sebelumnya

jika (1-0) maka (1-0)

Pada gambar diatas merupakan rangkaian dan simbol daripada RS FLIP-FLOP dan tabel kebenarannya yang mana perubahan pada input menyebabkan perubahan pada output jika (s) diberi logika (0) dan (R) diberi (1), maka pada output gate (1) / Q = 1, sehingga pada ke 2 input gate 2 akan sama, yaitu logika (1) hal ini akan menyebabkan output Q not atau gate 2 akan (0) kemudian diumpan balik ke gate (1) dan output dari gate (1) akan (1) sampai seterusnya dan untuk merubah keadaan tersebut, maka input R dan S harus diberikan input yang berbeda.

CLOCK SET RESET (RST) FLIP-FLOP

TABEL KEBENARAN

1 variasi dari bentuk dasar RS FF adalah bahwa rangkaian blocknya memiliki tambahan input yang diberi tanda clock input operasi kerja dari rangkaian ini identik dengan RS FF tetapi untuk mengoperasikannya harus ada clock input bila clock input pada logika nol, data dari SR (input) tidak akan dapat masuk kedalam rangkaian sehingga output tetap tidak berubah RST FF dapat ditriger dengan logika 1/0 bila input data dari S dan R masuk ke FF pada saat perubahan dari 0 ke 1 >>

, maka rangkaian tadi disebut "positif edge trigger" dan jika kebalikannya dari 1 ke 0, maka disebut "negatif edge trigger">>

, maka rangkaian tadi disebut "positif edge trigger" dan jika kebalikannya dari 1 ke 0, maka disebut "negatif edge trigger">>

SIMULASI GERBANG LOGIKA

PROBE CHECKER

Probe Checker merupakan implementasi dari gerbang logic dan dimanfaatkan sebagai alat untuk mendeteksi keberadaan signal digital didalam suatu rangkaian elektronika, dimana tegangan maksimum yang mampu dideteksi adalah 5 volt.

Teori Dasar dari :

- AND GATE = 7408

- OR GATE = 7432

- NOT GATE = 7404

- NAND GATE = 7400

- NOR GATE = 7402

Kondisi mengambang = 1, tanpa ada input, output = 0, LED OFF

Kondisi mengambang atau tanpa input = 0, tanpa output = 1, LED ON

DATA (D) FLIP-FLOP

Data FF dibentuk dari RST FF

Prinsip kerja :

Pada saat data S = 1 dan r = 0, maka data akan masuk membuat Q = 1 dan Q = 0 pada saat ada clock input yang perubahan di 0 ke 1 apabila data 0, maka membuat output Q = 0 dan Q = 1.

TOGGLE (T) FLIP-FLOP

JK FLIP - FLOP

Model operasi dari 3 FF ditentukan oleh input J dan K, misalnya kita berikan J dan K logika 1, maka FF akan berfungsi sebagai Toggle FF, sedangkan jika kita berikan logika 0 pada J dan K, maka output tidak akan berubah, untuk bekerja normal, maka Set dan Reset diberikan logika 1, jika clear/reset diberikan 0, maka output JK FF akan Reset = Q = 0 dan Q not = 1 dengan cara yang sama Reset input dapat digunakan untuk Set, yaitu Q = 1 dan Q not = 0.

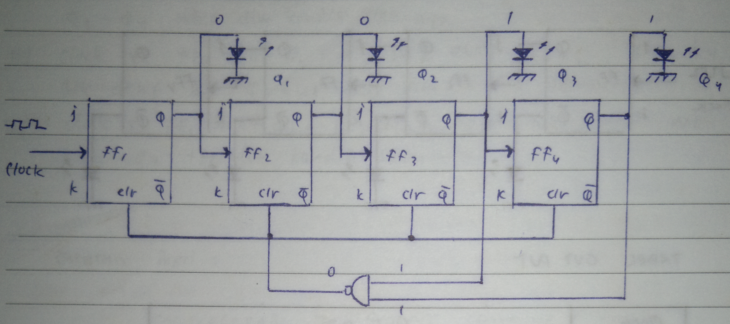

REGISTER GESER (RING COUNTER)

Prinsip kerja :

- masukan data = 1 pada FF, maka L1 sampai L4 OFF

- aktifkan clock, maka data akan dikeluarkan oleh FF dan L1 ON sedangkan L2 - L4 OFF

- masukan data 0 pada FF1 dan aktifkan clock, maka L1 OFF L2 ON, L3 dan L4 OFF

- clock aktif, L1 dan L2 OFF, L3 ON, L4 OFF

- clock aktif, L1, L2 dan L3 OFF, L4 ON

- clock aktif, L1 - L4 OFF.

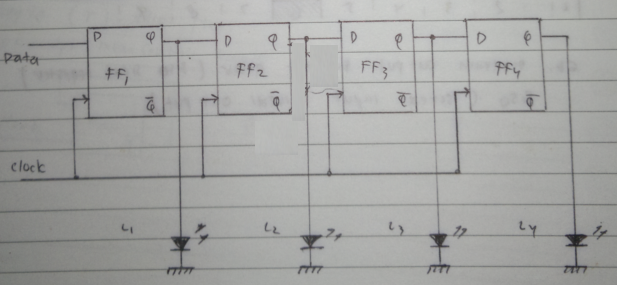

RING COUNTER (2)

Prinsip kerja :- masukan data = 1 pada FF1, maka L1 - L4 OFF

- clock 1 aktif, L1 ON, L1-L4 OFF

- S1 OFF, S2 ON, clock 2 ON, L2 ON, L1, L3 DAN L4 OFF

- clock 3 ON, L3 ON, L1, L2 DAN L4 OFF

- clock 4 ON, L4 ON, L1-L3 OFF

- clock 5 ON, Kembali pada clock 1 (keadaan sama dengan no.2)

- clock 6 ON, kembali pada clock 2 (keadaan sama dengan no.3)

- clock 7 ON, kembali pada clock 3 (keadaan sama dengan no.4)

- clock 8 ON, kembali pada clock 4 (keadaan sama dengan no.5)

- pola seperti ini akan berjalan terus, sementara itu untuk menampilkan sebuah ring counter, maka disusun hingga membentuk lingkaran. maka disebutlah "Ring Counter".